DRAM和NAND如何演进?

近年来,因为技术的发展,大家认为DRAM和NAND逐渐走向了困境,那么存储技术未来该如何发展。以下是专家的分享。

扩展 3D NAND

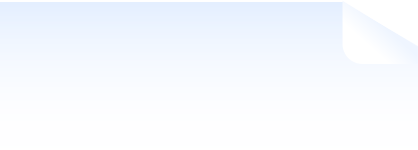

3D NAND 现在在 PC、移动设备和数据中心中无处不在,并且正在迅速进入汽车和神经网络应用。3D 配置中的电荷捕获闪存 (CTF) 通过堆叠字线、使用大量沉积、蚀刻、填充和退火步骤以及更少的光刻图案化步骤(相对于逻辑)以低成本扩展。位密度每年大幅增加 30%。

为了显著减小裸片尺寸,所有领先的 NAND 制造商都开始在存储器阵列下方制造 CMOS 外围电路。三星率先在 2010 年左右将其外围单元 (COP) V-NAND 推向市场,显著缩小了裸片尺寸。但增加位密度背后的持续缩放引擎是重复的层堆栈——使用多个沉积步骤、高纵横比蚀刻和高 AR 填充能力来加速阵列(层)中存储字线的数量。三星、美光和海力士的这些层数超过 200,它们都制定了到 2030 年达到 1,000 层的路线图。

Russ Meyer 和 Micron 的同事在最近的 IEDM 上讨论了几个可以进一步提高 NAND 位密度和性能的旋钮,包括替代块架构、新的单元薄膜和间距缩放选项。“3D NAND 继续提供甚至加速数据行业所需的 NAND 缩放趋势,部分原因是其更大的栅极面积和改进的环栅 (GAA) 架构的静电。” 继续沿着这条道路前进,将在未来 5 到 6 年内实现 1,000 层,芯片厚度接近 100µm,这对许多应用来说是无法接受的。”

通过增加 50% 以上的 WL 层(字线充当栅极并围绕pillar状沟道),该结构可能会出现摆动和不稳定。这反过来又会导致诸如字线泄漏、单元形成问题和位线接触未对准之类的故障。美光正在探索的一种策略是将 9 pillar更改为 19 pillar,其结构宽度约为 2 倍,并且与多家制造商使用的当前 4 pillar选择门(子块)的块架构兼容(见图 1)。这一变化使单元面积减少了 9%。

图1:从传统的 9 结构(pillar行/块)到 19 pillar的变化相关的 NAND 阵列缩放可使块缩小 9%,这与 4 pillar子块兼容。

XY 缩放在平面 NAND 中遇到了极限,而 3D NAND 正在接近它。其他问题包括由电池间耦合(即噪声)引起的器件退化。第一步,WL 栅极替换,对于 19 柱更宽的块架构变得更具挑战性。牺牲层去除和 WL 金属填充的纵横比较大,导致较差的金属台阶覆盖(和较高的 WL 电阻),以及空隙和接缝中的卤素污染。该小组发现,更薄的替代阻挡层金属可以更好地防止卤素杂质,从而降低块状钨填充物的电阻率。

阵列高度的增加也可以通过单元间距缩放来减轻,使柱之间的间距。蚀刻纵横比确实随着间距的缩小而适度增加,但更大的问题是在减小的沟道宽度下对读取性能的影响,这需要新的集成方案。

美光团队进一步表示,未来的 NAND 每个单元可以包含超过 4 位。然而,相对于体积位密度的增加,每个单元更多的位会导致每个状态的电子数量损失更大。“首先将电池设备的尺寸(例如,最好是柱间距 XY 缩放)缩放到工艺能力的极限更为合理。创新的块架构和 WL 驱动程序方案是未来节点的 3D NAND 性能可扩展性的关键,”他们总结道。

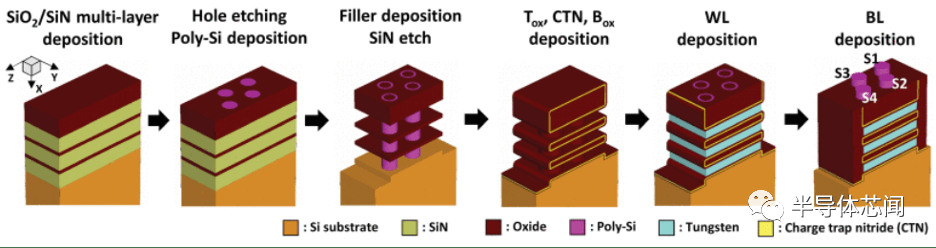

随着公司继续扩展 3D NAND,他们正在观察 3D 闪存结构中的应力分布与电气性能之间的关系。正如浦项科技大学和三星的论文所述,这些结构由隧道氧化物、电荷捕获氮化物、钨和多晶硅通道组成,因此不同材料之间的晶格失配和热失配会导致机械应力(见图 2)。热退火确实会导致一些松弛,但这些日益受限的 3D NAND 结构中的净机械应力仍然会对电气性能产生很大影响。

图 2:多重沉积、高纵横比蚀刻和填充步骤创建电荷捕获 NAND 三明治

有趣的是,模拟确定降低钨的沉积温度具有最显著的影响,因为钨施加的应力远远超过其他薄膜施加的应力,并且对沟道应力的影响最大(见图 3)。通过降低钨沉积温度(和应力),多晶硅沟道的导带和价带移动,有效地提高了性能。

图 3:多晶硅 (a)、钨 (b)、氧化层 (c) 和电荷陷阱氮化物 (d) 的平均沟道应力与导通电流变化的关系。

研究人员强调,相对于隧道氧化物 (SiO 2 ) 和多晶硅,电荷陷阱氮化物和钨具有更高的 CTE(热膨胀系数)。提高钨和氮化物沉积温度可有效地诱导压应力并降低导通电流,而不会影响器件的存储器工艺窗口和阈值电压。进一步的模拟表明,降低钨沉积温度是提高 NAND 性能的最佳手段。

有了所有这些窄的、高深宽比的孔,间隙填充成为 3D NAND 的关键需求也就不足为奇了——尤其是因为沉积温度在 300°C 到 900°C 范围内。最近开发的一个例子是来自 Brewer Science 的旋涂碳材料,它已被用于填充 0.5 x 10μm 的沟槽,在 550°C 下热处理 60 分钟后没有出现薄膜空洞、开裂或分层的迹象。[热稳定的旋涂碳表现出最小的收缩和质量损失。旋涂后,它使用软烘烤和热板固化,然后根据需要进行炉内氮化。

为 AI、汽车扩展 DRAM

机器学习和 AI 以及汽车领域的应用快速增长,需要增加 DRAM 的带宽。这些外围电路执行不同的功能(即行/列解码器、读出放大器、I/O 数据缓冲器),因此需要具有低栅极泄漏、关断电流和高击穿电压以及 DRAM 工艺兼容性的优化晶体管。即使对于多晶硅/氧化物平面 FET 也是如此。在使用高 k 金属栅极的 finFET 晶体管中,必须优化流程以承受长时间的高温退火(550°C 下 4 小时)并保持电气特性。

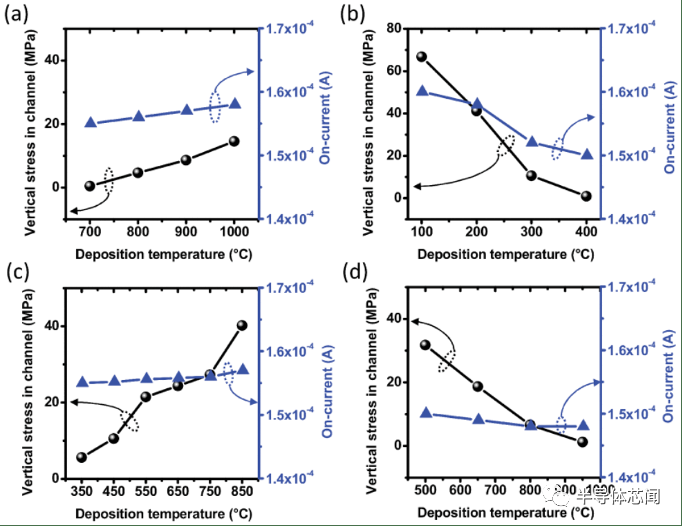

图 4:与后栅极高 k 替代金属栅极工艺(右)相比,先栅极扩散和栅极置换(左)导致更高的阈值电压和更少的用于功函数调整的金属栅极选项

imec 的 Elena Capogreco 及其同事最近展示了一种 14 纳米高 k / 金属栅极替换栅极方法,该方法可以在承受长时间退火的同时实现低于 0.2V 的 nMOS 阈值电压。[“除了减少热预算外,与栅极优先扩散和栅极替换方案(见图 4)相比,使用 RMG 流程的另一个优势是增加了 nMOS 和 nMOS 之间 WFM(功函数金属)工程的自由度。”

研究人员解释说,虽然用于外围 DRAM 电路的低成本 CMOS finFET 中的栅极优先 HKMG 已经实现,但由于高温退火引起的费米能级钉扎(特别是在 pMOS 器件上),阈值电压相对较高. 新的热稳定栅极堆叠包括 1nm 界面氧化物、1.9nm 氧化铪、2nm TiN、5nm TiAl、3nm TiN 以及钨 CVD 和 CMP。

目标栅极长度为 30nm。吸取的一些工艺教训包括需要用氮化硅覆盖钨以抑制退火引起的栅极氧化物退化。CMP 之后的氮化物覆盖进一步封装了金属。通过在氮气中对氧化铪进行退火,然后进行牺牲硅盖退火以提高其热稳定性,优化了 nMOS 的有效功函数。对于镧偶极栅叠层,6 埃 LaO 通过 ALD 沉积,并用 2nm TiN 和 5nm 牺牲 a-Si 覆盖。a-Si 的推进退火和湿法去除在 TiAl 和 W 下留下 TiN。加盖的栅极堆叠经受了 4 小时的 550° 至 600°C 退火。最终有效功函数为 4.4eV,栅极泄漏减少,有效氧化层厚度为 14 埃。使用环形振荡器和 SRAM 演示了性能。

结论

3D NAND 缩放一直是移动设备功能的福音,芯片制造商正在继续堆叠字线层以提高性能和位密度。最终,NAND 设备可能需要替代材料、新配置,甚至每个单元超过四位。

与此同时,5G SoC 继续为手机用户带来高性能和长续航,似乎没有任何直接限制。然而,这一切都不容易。晶体管和互连优化都是扩展到 5nm 及更高工艺的关键,而针对低功耗和低泄漏优化的外围 DRAM 电路对高热预算工艺更为敏感。好消息是功函数调整和更换高 k 金属栅极似乎是推动因素。

(来源:半导体芯闻)